THÈSE

Pour obtenir le grade de

# DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES

École doctorale : MSTII - Mathématiques, Sciences et technologies de l'information, Informatique Spécialité : Informatique

Unité de recherche : Centre de recherche Inria de l'Université Grenoble Alpes

Vers une caractérisation automatique du comportement microarchitectural pour la modélisation des performances de noyaux de calcul : une analyse des micro-architectures Cortex A72 et Intel

# Towards automatic characterization of microarchitectural behaviour for performance modeling of computing kernels: an analysis of the Cortex A72 and Intel microarchitectures

Présentée par :

# **Théophile BASTIAN**

Direction de thèse :

Fabrice RASTELLO DIRECTEUR DE RECHERCHE, INRIA CENTRE GRENOBLE-RHONE-ALPES Directeur de thèse

#### Rapporteurs :

KEVIN MARTIN PROFESSEUR DES UNIVERSITES, UNIVERSITE BRETAGNE SUD - LORIENT VANNES GABRIEL RODRIGUEZ ASSOCIATE PROFESSOR, UNIVERSIDAD DA CORUÑA

Thèse soutenue publiquement le 9 décembre 2024, devant le jury composé de :

| LAURENCE PIERRE,                                      | Présidente         |

|-------------------------------------------------------|--------------------|

| PROFESSEUR DES UNIVERSITES, UNIVERSITE GRENOBLE ALPES |                    |

| FABRICE RASTELLO,                                     | Directeur de thèse |

| DIRECTEUR DE RECHERCHE, CENTRE INRIA UNIVERSITE       |                    |

| GRENOBLE ALPES                                        |                    |

| KEVIN MARTIN,                                         | Rapporteur         |

| PROFESSEUR DES UNIVERSITES, UNIVERSITE BRETAGNE SUD - |                    |

| LORIENT VANNES                                        |                    |

| GABRIEL RODRIGUEZ,                                    | Rapporteur         |

| ASSOCIATE PROFESSOR, UNIVERSIDAD DA CORUÑA            |                    |

| GAËL THOMAS,                                          | Examinateur        |

| DIRECTEUR DE RECHERCHE, CENTRE INRIA DE SACLAY        |                    |

|                                                       |                    |

Version 6b0539a

#### Résumé

Qu'il s'agisse de calculs massifs distribués sur plusieurs baies, de calculs en environnement contraint — comme de l'embarqué ou de l'*edge computing* — ou encore de tentatives de réduire l'empreinte écologique d'un programme fréquemment utilisé, de nombreux cas d'usage justifient l'optimisation poussée d'un programme. Celle-ci s'arrête souvent à l'optimisation de haut niveau (algorithmique, parallélisme, …), mais il est possible de la pousser jusqu'à une optimisation bas-niveau, s'intéressant à l'assembleur généré en regard de la microarchitecture du processeur précis utilisé.

Une telle optimisation demande une compréhension fine des aspects à la fois logiciels et matériels en jeu, et n'est bien souvent accessible qu'aux experts du domaine. Les *code analyzers* (analyseurs de code), cependant, permettent d'abaisser le niveau d'expertise nécessaire pour accomplir de telles optimisations, en automatisant une partie du travail de compréhension des problèmes de performance rencontrés. Ces mêmes outils permettent également aux experts d'être plus efficaces dans leur travail.

Dans ce manuscrit, nous étudierons les principaux facteurs limitants de la performance d'un processeur, sur lesquels la précision des outils de l'état de l'art est bien souvent inégale. Nous apportons, sur chacun de ces facteurs limitants, une contribution nouvelle : automatisation de l'obtention d'un modèle du *backend*, étude manuelle du *frontend* en vue de l'automatisation de son modèle, et extraction automatique des dépendances à *travers la mémoire* d'un noyau de calcul. Nous apportons également une étude systématique et automatisée des performances de prédiction de différents *code analyzers* de l'état de l'art.

#### Abstract

Be it massively distributed computation over multiple server racks, constrained computation — such as in embedded environments or in *edge computing* —, or still an attempt to reduce the ecological footprint of a frequently-run program, many use-cases make it relevant to deeply optimize a program. This optimisation is often limited to high-level optimisation — choice of algorithms, parallel computing, ... Yet, it is possible to carry it further to low-level optimisations, by inspecting the generated assembly with respect to the microarchitecture of the specific microprocessor used to fine-tune it.

Such an optimisation level requires a very detailed understanding of both the software and hardware aspects implied, and is most often the realm of experts. *Code analyzers*, however, are tools that help lowering the expertise threshold required to perform such optimisations by automating away a portion of the work required to understand the source of the encountered performance problems. The same tools are also useful to experts, as they help them be more efficient in their work.

In this manuscript, we study the main performance bottlenecks of a processor, on which the state of the art does not perform consistently. For each of these bottlenecks, we contribute to the state of the art. We work on automating the obtention of a model of the processor's *backend*; we manually study the processor's *frontend*, hoping to set a milestone towards the automation of the obtention of such models; we provide a tool to automatically extract a computation kernel's *memory-carried* dependencies. We also provide a systematic, automated and fully-tooled study of the prediction accuracy of various state-of-the-art code analyzers.

#### Remerciements

Cette thèse n'aurait très certainement pas été la même sans la présence à mes côtés et l'aide précieuse de nombreuses personnes, que je souhaite remercier chaleureusement ici.

À commencer, bien évidemment, par Fabrice, sans qui ce manuscrit n'aurait tout bonnement pas existé, et qui m'a accompagné dans mon parcours, de la découverte de ce domaine à la soutenance de cette thèse.

Merci également au jury, et encore plus aux deux rapporteurs, Kevin Martin et Gabriel Rodriguez, de s'être plongés dans ce manuscrit. Merci pour vos commentaires positifs et encourageants, mais aussi pour vos retours critiques qui me permettent d'améliorer ce travail.

Plus largement, c'est aussi toute l'équipe CORSE que je souhaite remercier, tant pour les échanges scientifiques constructifs que nous avons pu avoir que pour les conversations plus légères de tous les jours qui ont fait du labo un endroit agréable<sup>1</sup>. Parmi vous, merci tout particulièrement à Nicolas D. pour notre collaboration sur Palmed que nous avons su, malgré les confinements et couvre-feux de cette étrange période, rentre motivante et productive. Merci aussi à Hugo P., Valentin T. et Christophe G., avec qui j'ai le plus directement collaboré. Merci encore à Imma P., qui sait si efficacement rendre la charge administrative transparente à nos yeux. Travailler avec vous tous et toutes a été un plaisir.

Mes remerciements vont aussi à la Ville d'Échirolles, et tout particulièrement à Philippe et Nicolas, qui m'ont permis de finir ma thèse dans de bonnes conditions malgré mon emploi à temps plein.

Toutes ces courbes et ces modèles n'auraient pas pu voir le jour sans l'exploitation forcenée de quelques pauvres processeurs, qui, je n'en doute pas, espéraient plutôt couler de doux jours dans un serveur web. Merci donc à Pinocchio, Dracula, les Dahus de Grid5000, et mes sincères excuses à Corse-rpi0 pour les pics de fièvre que je lui ai causés<sup>2</sup>.

Il va également sans dire que la présence et le soutien de mes proches de tous horizons m'a été précieux au cours de ces années, et je vous remercie chaleureusement toutes et tous. Au risque d'oublier des gens, je citerai pêle-mêle mes amis de l'ENS et de l'Arcoloc, les choristes et amis des Rainbow et, plus tard, du CUG et les personnes rencontrées à Grésille. Et, surtout, un merci tout particulier à Sarah, Nina et à ma mère, Rosine.

Merci à vous toutes et tous.

<sup>1.</sup> Même s'il y manquait du vrai café.

<sup>2.</sup> Et mon manque d'inspiration pour son baptême.

# Contents

| No       | Notations 8  |                                                                                              |           |  |  |  |  |  |

|----------|--------------|----------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|

| In       | trodu        | action                                                                                       | 9         |  |  |  |  |  |

| 1        | Fou          | ndations                                                                                     | <b>12</b> |  |  |  |  |  |

|          | 1.1          | A dive into processors' microarchitecture                                                    | 12        |  |  |  |  |  |

|          |              | 1.1.1 High-level abstraction of processors                                                   | 12        |  |  |  |  |  |

|          |              | 1.1.2 Microarchitectures                                                                     | 13        |  |  |  |  |  |

|          | 1.2          | Kernel optimization and code analyzers                                                       | 16        |  |  |  |  |  |

|          |              | 1.2.1 Code analyzers                                                                         | 17        |  |  |  |  |  |

|          |              | 1.2.2 Examples with llvm-mca                                                                 | 18        |  |  |  |  |  |

|          |              | 1.2.3 Definitions                                                                            | 23        |  |  |  |  |  |

|          | 1.3          | State of the art                                                                             | 28        |  |  |  |  |  |

|          |              | 1.3.1 Manufacturer-sourced data                                                              | 28        |  |  |  |  |  |

|          |              | 1.3.2 Third-party instruction data                                                           | 28        |  |  |  |  |  |

|          |              | 1.3.3 Code analyzers and their models                                                        | 29        |  |  |  |  |  |

| <b>2</b> | Palm         | ed: automatically modelling the backend                                                      | 31        |  |  |  |  |  |

| -        | 2.1          | Resource models                                                                              | 31        |  |  |  |  |  |

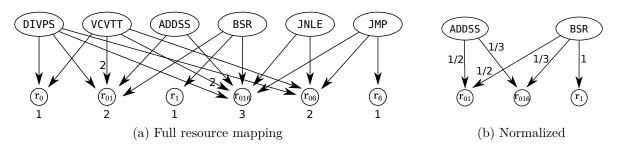

|          | 2.1          | 2.1.1 Usual representation: tripartite disjunctive graph                                     | 31        |  |  |  |  |  |

|          |              | 2.1.2 Dual representation: conjunctive resource mapping                                      | 33        |  |  |  |  |  |

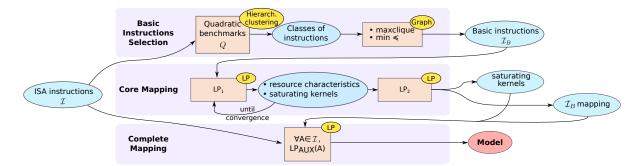

|          | 2.2          | Palmed design                                                                                | 34        |  |  |  |  |  |

|          | 2.2          | Measuring a kernel's throughput: Pipedream                                                   | 35        |  |  |  |  |  |

|          | $2.0 \\ 2.4$ | Finding basic blocks to evaluate Palmed                                                      | 36        |  |  |  |  |  |

|          | 2.1          | 2.4.1       Benchmark suites                                                                 | 37        |  |  |  |  |  |

|          |              | 2.4.2 Manually extracting basic blocks                                                       | 37        |  |  |  |  |  |

|          |              | 2.4.2     Manually extracting basic blocks       2.4.3     Automating basic block extraction | 37        |  |  |  |  |  |

|          | 2.5          | Evaluating Palmed                                                                            | 39        |  |  |  |  |  |

|          | 2.0          | 2.5.1 Evaluation harness                                                                     | 39        |  |  |  |  |  |

|          |              | 2.5.2 Metrics extracted                                                                      | 40        |  |  |  |  |  |

|          |              | 2.5.2 Methos extracted                                                                       | 40        |  |  |  |  |  |

|          | 2.6          | Other contributions                                                                          | 40<br>42  |  |  |  |  |  |

|          | _            |                                                                                              |           |  |  |  |  |  |

| 3        | -            | ond ports: manually modelling the A72 frontend                                               | 44        |  |  |  |  |  |

|          | 3.1          | Necessity to go beyond ports                                                                 | 45        |  |  |  |  |  |

|          | 3.2          | The Cortex A72 CPU                                                                           | 45        |  |  |  |  |  |

|          | 3.3          | Manually modelling the A72 frontend                                                          | 47        |  |  |  |  |  |

|          |              | 3.3.1 Finding micro-operation count for each instruction                                     | 47        |  |  |  |  |  |

|          |              | 3.3.2 Bubbles in the pipeline                                                                | 49        |  |  |  |  |  |

|          | 3.4          | Evaluation on Palmed                                                                         | 53        |  |  |  |  |  |

|          | 3.5          | A parametric model for future works of automatic frontend model generation .                 | 53        |  |  |  |  |  |

| 4  | A n   | nore systematic approach to throughput prediction performance analysis: |           |

|----|-------|-------------------------------------------------------------------------|-----------|

|    | Cesl  | ASMe                                                                    | <b>57</b> |

|    | 4.1   | Re-defining the execution time of a kernel                              | 58        |

|    | 4.2   | Related works                                                           | 59        |

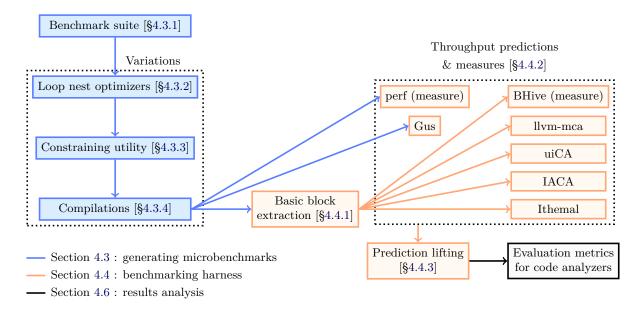

|    | 4.3   | Generating microbenchmarks                                              | 60        |

|    |       | 4.3.1 Benchmark suite                                                   | 60        |

|    |       | 4.3.2 C-to-C loop nest optimizers                                       | 61        |

|    |       | 4.3.3 Constraining utility                                              | 61        |

|    |       | 4.3.4 C-to-binary compiler                                              | 61        |

|    | 4.4   | Benchmarking harness                                                    | 61        |

|    |       | 4.4.1 Basic block extraction                                            | 62        |

|    |       | 4.4.2 Throughput predictions and measures                               | 62        |

|    |       | 4.4.3 Prediction lifting and filtering                                  | 62        |

|    | 4.5   | Experimental setup and evaluation                                       | 63        |

|    | 1.0   | 4.5.1 Experimental environment                                          | 63        |

|    |       | 4.5.2 Comparability of the results                                      | 63        |

|    |       | 4.5.3 Relevance and representativity (bottleneck analysis)              | 65        |

|    |       | 4.5.4 Carbon footprint                                                  | 65        |

|    | 4.6   | Results analysis                                                        | 66        |

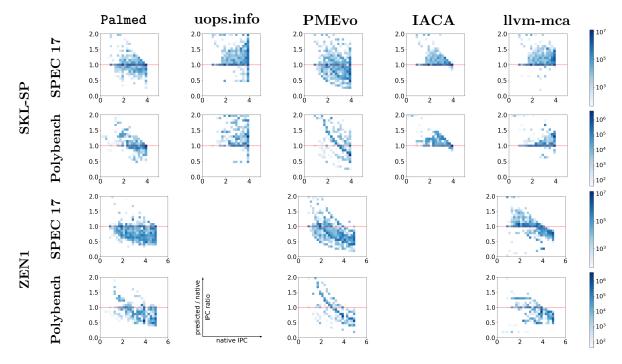

|    | 1.0   | 4.6.1 Throughput results                                                | 66        |

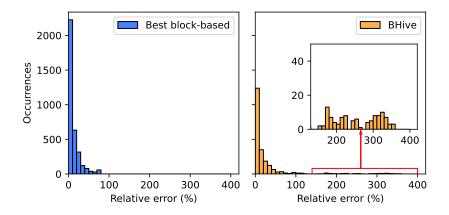

|    |       | 4.6.2 Understanding BHive's results                                     | 66        |

|    |       | 4.6.3 Bottleneck prediction                                             | 68        |

|    |       | 4.6.4 Impact of dependency-boundness                                    | 69        |

|    |       |                                                                         | 05        |

| 5  | Stat  | tic extraction of memory-carried dependencies                           | 73        |

|    | 5.1   | Types of dependencies                                                   | 73        |

|    | 5.2   | A baseline: dynamic dependencies detection with valgrind                | 75        |

|    |       | 5.2.1 Valgrind                                                          | 75        |

|    |       | 5.2.2 Depsim                                                            | 75        |

|    | 5.3   | Static dependencies detection                                           | 76        |

|    |       | 5.3.1 Far-reaching dependencies do not impact performance               | 77        |

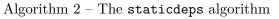

|    | 5.4   | Staticdeps                                                              | 79        |

|    |       | 5.4.1 The staticdeps heuristic                                          | 79        |

|    |       | 5.4.2 Practical implementation                                          | 81        |

|    |       | 5.4.3 Limitations                                                       | 81        |

|    | 5.5   | Evaluation                                                              | 82        |

|    |       | 5.5.1 Comparison to depsim results                                      | 82        |

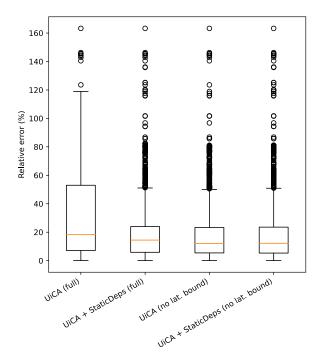

|    |       | 5.5.2 Enriching uiCA's model                                            | 84        |

|    |       | 5.5.3 Analysis speed                                                    | 86        |

|    |       |                                                                         |           |

| 6  | Wra   | apping it all up                                                        | 88        |

|    | 6.1   | Critical path model                                                     | 88        |

|    | 6.2   | Evaluation                                                              | 88        |

|    | 6.3   | Towards a modular approach?                                             | 90        |

| Co | onclu | Ision                                                                   | 91        |

| Bi | blio  | graphy                                                                  | 94        |

|    | - 6   |                                                                         | -         |

# Notations

Throughout this whole document, the following non-standard notations are used.

| Notation                              | Meaning                                                                                                                                                                                                          | (See also)         |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| $\overline{\mathcal{K}}$              | Reciprocal throughput of $\mathcal{K}$ , in cycles per occurrence of $\mathcal{K}$ .                                                                                                                             | <b>§</b> 1.2.3     |

| $\overline{\mathcal{K}}^{M(n)}$       | Measured reciprocal throughput of $\mathcal{K}$ , over <i>n</i> iterations of $\mathcal{K}$ .<br>When there is no ambiguity and <i>n</i> is sufficiently large, we often write $\overline{\mathcal{K}}$ instead. | <b>§1</b> .2.3     |

| $\overline{\mathcal{K}}^{\mathbf{B}}$ | Reciprocal throughput of $\mathcal{K}$ if it was only limited by the CPU's backend.                                                                                                                              | §3.3.1             |

| $\overline{\mathcal{K}}^{\mathbf{F}}$ | Reciprocal throughput of $\mathcal{K}$ if it was only limited by the CPU's frontend.                                                                                                                             | §3.3.1             |

| $C(\mathcal{K})$                      | Number of cycles of a kernel $\mathcal{K}$ .                                                                                                                                                                     | \$1.2.3            |

| $\mathcal{K}^n$                       | $\mathcal{K}$ repeated $n$ times.                                                                                                                                                                                | \$1.2.3            |

| $\operatorname{IPC}(\mathcal{K})$     | Instructions Per Cycle in the execution of the kernel $\mathcal{K}$ , in steady state, averaged.                                                                                                                 | <b>§</b> 1.2.3     |

| $\#_{\mu}i$                           | Number of $\mu$ OPs the instruction <i>i</i> is decoded into. This can be extended to a kernel: $\#_{\mu}\mathcal{K}$ .                                                                                          | §3.3.1             |

| $	au_K$                               | Kendall's $\tau$ coefficient of correlation.                                                                                                                                                                     | §2.5.2,<br>[Ken38] |

# Introduction

Developing new features and fixing problems are often regarded as the major parts of the development cycle of a program. However, performance optimization might be just as crucial for compute-intensive software. On small-scale applications, it improves usability by reducing, or even hiding, the waiting time the user must endure between operations, or by allowing heavier workloads to be processed without needing larger resources or in constrained embedded hardware environments. On large-scale applications, that may run for an extended period of time, or may be run on whole clusters, optimization is a cost-effective path, as it allows the same workload to be run on smaller clusters, for reduced periods of time.

The most significant optimisation gains come from "high-level" algorithmic changes, such as computing on multiple cores instead of sequentially, caching already computed results, reimplementing a function to run asymptotically in  $\mathcal{O}(n \cdot \log(n))$  instead of  $\mathcal{O}(n^2)$  or avoiding the copy of large data structures. However, when a software is already well-optimized from these perspectives, the impact of low-level considerations, stemming from the hardware implementation of the machine itself, cannot be neglected anymore. A common example of such impacts is the iteration of a large matrix either row-major or column-major:

| $\operatorname{sum} \leftarrow 0$        | $\operatorname{sum} \leftarrow 0$       |

|------------------------------------------|-----------------------------------------|

| for $row < MAX_ROW do$                   | for $col < MAX\_COLUMN do$              |

| $for col < MAX\_COLUMN do$               | for $row < MAX_ROW do$                  |

| $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $ | $sum \leftarrow sum + matrix[row][col]$ |

While both programs are performing the exact same computation, the left one iterates on rows first, or *row-major*, while the right one iterates on columns first, or *column-major*. The latter, on large matrices, will cause frequent cache misses, and was measured to run up to about six times slower than the former [Bas23].

This, however, is still an optimization that holds for the vast majority of CPUs. In many cases, transformations targeting a specific microarchitecture can be very beneficial. For instance, Uday Bondhugula found out that manual tuning, through many techniques and tools, of a general matrix multiplication could multiply its throughput by roughly 13.5 compared to gcc -03, or even be 130 times faster than clang -03 [Bon20]. This kind of optimizations, however, requires manual effort, and a deep expert knowledge both in optimization techniques and on the specific architecture targeted. These techniques are only worth applying on the parts of a program that are most executed — usually called the *hottest* parts —, loop bodies that are iterated enough times to be assumed infinite. Such loop bodies are called *computation kernels*, with which this whole manuscript will be concerned.

Developers are used to *functional debugging*, the practice of tracking the root cause of an unexpected bad functional behaviour. Akin to it is *performance debugging*, the practice of tracking the root cause of a performance below expectations. Just as functional debugging can be carried in a variety of ways, from guessing and inserting print instructions to sophisticated tools such as gdb, performance debugging can be carried with different tools. Crude timing measures and profiling can point to a general part of the program or hint an issue; reading *hardware counters* — metrics reported by the CPU — can lead to a better understanding, and

may confirm or invalidate an hypothesis. Other tools still, *code analyzers*, analyze the assembly code and, in the light of a built-in hardware model, strive to provide a performance analysis.

An exact modelling of the processor would require a cycle-accurate simulator, reproducing the precise behaviour of the silicon, allowing one to observe any desired metric. Such a simulator, however, would be prohibitively slow, and is not available on most architectures anyway, as processors are not usually open hardware and the manufacturer regards their implementation as industrial secret. Code analyzers thus resort to approximated, higher-level models of varied kinds. Tools based on such models, as opposed to measures or hardware counters sampling, may not always be precise and faithful. They can, however, inspect at will their inner model state, and derive more advanced metrics or hypotheses, for instance by predicting which resource might be overloaded and slow the whole computation.

In this thesis, we explore the three major aspects that work towards a code analyzer's accuracy: a *backend model*, a *frontend model* and a *dependencies model*. We propose contributions to strengthen them, as well as to automate the underlying models' synthesis. We focus on *static* code analyzers, that derive metrics, including runtime predictions, from an assembly code or assembled binary without executing it.

The first chapter introduces the foundations of this manuscript, describing the microarchitectural notions on which our analyses will be based, and exploring the current state of the art.

The chapter 2 introduces Palmed, a benchmarks-based tool automatically synthesizing a model of a CPU's backend. Although the theoretical core of Palmed is not my own work, I made major contributions to other aspects of the tool. The chapter also presents the foundations and methodologies Palmed shares with the following parts.

In chapter 3, we explore the frontend aspects of static code analyzers. This chapter focuses on the manual study of the Cortex A72 processor, and proposes a static model of its frontend. We finally reflect on the generalization of our manual approach into an automated frontend modelling tool, akin to Palmed.

Chapter 4 makes an extensive study of the state-of-the-art code analyzers' strengths and shortcomings. To this end, we introduce a fully-tooled approach in two parts: first, a benchmarkgeneration procedure, yielding thousands of benchmarks relevant in the context of our approach; then, a benchmarking harness evaluating code analyzers on these benchmarks. We find that most state-of-the-art code analyzers struggle to correctly account for some types of data dependencies.

Further building on our findings, chapter 5 introduces staticdeps, an accurate heuristicbased tool to statically extract data dependencies from an assembly computation kernel. We extend uiCA, a state-of-the-art code analyzer, with staticdeps predictions, and evaluate the enhancement of its accuracy.

Throughout this manuscript, we explore notions that are transversal to the hardware blocks the chapters lay out.

Most of our approaches work towards an *automated*, *microarchitecture-independent* tooling. While fine-grained, accurate code analysis is directly concerned with the underlying hardware and its specific implementation, we strive to write tooling that has the least dependency towards vendor-specific interfaces. In practice, this rules out most uses of hardware counters, which depend greatly on the manufacturer, or even the specific chip considered. As some CPUs expose only very bare hardware counters, we see this commitment as an opportunity to develop methodologies able to model these processors.

This is particularly true of Palmed, in chapter 2, whose goal is to model a processor's backend resources without resorting to its vendor-specific hardware counters. Our frontend study, in chapter 3, also follows this strategy by focusing on a processor whose hardware counters give little to no insight on its frontend. While this goal is less relevant to **staticdeps**, we rely on external libraries to abstract the underlying architecture.

Our methodologies are, whenever relevant, *benchmarks- and experiments-driven*, in a bottomup style, placing real hardware at the center. In this spirit, Palmed is based solely on benchmarks, discarding entirely the manufacturer's documentation. Our model of the Cortex A72 frontend is based both on measures and documentation, yet it strives to be a case study from which future works can generalize, to automatically synthesize frontend models in a benchmarks-based fashion. One of the goals of our survey of the state of the art, in chapter 4, is to identify through experiments the shortcomings that are most crucial to address in order to strengthen static code analyzers.

Finally, against the extent of the ecological and climatic crises we are facing, as assessed among others by the IPCC [Con23], we believe that every field and discipline should strive for a positive impact or, at the very least, to reduce as much as possible its negative impact. Our very modest contribution to this end, throughout this thesis, is to commit ourselves to computations as *frugal* as possible: run computation-heavy experiments as least as possible; avoid running multiple times the same experiment, but cache results instead when this is feasible; etc. This commitment partly motivated us to implement a results database in **Palmed**, to compute only once each benchmark. As our experiments in chapter 4 take many hours to yield a result, we at least evaluate their carbon impact.

We believe it noteworthy, however, to point out that although this thesis is concerned with tools that help optimize large computation workloads, *optimization does not lead to frugality*. In most cases, Jevons paradox — also called rebound effect — makes it instead more likely to lead to an increased absolute usage of computational resources [Jev66; YM16].

# Chapter 1

# **Foundations**

Code analyzers lay at the boundary of program analysis and microarchitectural knowledge. In order to understand their internal models, and how they derive performance metrics from them, notions on both of those worlds are needed.

This first chapter aims to lay the foundations for this manuscript. To this end, we first go over a coarse-grained view of the microarchitectural details of the parts of a modern processor relevant to our works. We then introduce notions and metrics on program analysis that will be used throughout this thesis. Finally, we summarize the current state of the art in the field of code analyzers, and relevant neighbouring topics.

## 1.1 A dive into processors' microarchitecture

A modern computer can roughly be broken down into a number of functional parts: a processor, a general-purpose computation unit; accelerators, such as GPUs, computation units specialized on specific tasks; memory, both volatile but fast (RAM) and persistent but slower (SSD, HDD); hardware specialized for interfacing, such as networks cards or USB controllers; power supplies, responsible for providing smoothed, adequate electric power to the previous components.

This manuscript will largely focus on the processor. While some of the techniques described here might possibly be used for accelerators, we did not experiment in this direction, nor are we aware of efforts in this direction.

#### 1.1.1 High-level abstraction of processors

A processor, in its coarsest view, is simply a piece of hardware that can be fed with a flow of instructions, which will, each after the other, modify the machine's internal state.

The processor's state, the available instructions themselves and their effect on the state are defined by an *Instruction Set Architecture*, or ISA; such as x86-64 or A64 (ARM's ISA). More generally, the ISA defines how software will interact with a given processor, including the registers available to the programmer, the instructions' semantics — broadly speaking, as these are often informal —, etc. These instructions are represented, at a human-readable level, by *assembly code*, such as add (%rax), %rbx in x86-64. Assembly code is then transcribed, or *assembled*, to a binary representation in order to be fed to the processor — for instance, 0x480318 for the previous instruction. This instruction computes the sum of the value held at memory address %rax and of the value %rbx, but it does not, strictly speaking, *return* or *produce* a result: instead, its stores the result of the computation in register %rbx, altering the machine's state.

This state, generally, is composed of a small number of *registers*, small pieces of memory on which the processor can directly operate — to perform arithmetic operations, index the main memory, etc. It is also composed of the whole memory hierarchy, including the persistent

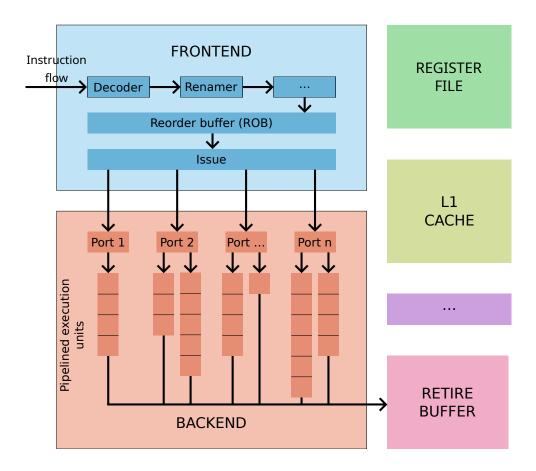

Figure 1.1 – Simplified and generalized global representation of a CPU microarchitecture

memory, the main memory (usually RAM) and the hierarchy of caches between the processor and the main memory. This state can also be extended to encompass external effects, such as networks communication, peripherals, etc.

The way an ISA is implemented, in order for the instructions to alter the state as specified, is called a *microarchitecture*. Many microarchitectures can implement the same ISA, as it is the case for instance with the x86-64 ISA, implemented both by Intel and AMD, each with multiple generations, which translates into multiple microarchitectures. It is thus frequent for ISAs to have many extensions, which each microarchitecture may or may not implement.

#### 1.1.2 Microarchitectures

While many different ISAs are available and used, and even many more microarchitectures are industrially implemented and widely distributed, some generalities still hold for the vast majority of processors found in commercial or server-grade computers. Such a generic view is obviously an approximation and will miss many details and specificities; it should, however, be sufficient for the purposes of this manuscript.

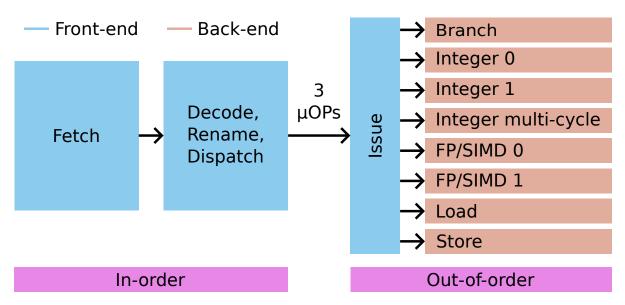

A microarchitecture can be broken down into a few functional blocks, shown in Figure 1.1, roughly amounting to a *frontend*, a *backend*, a *register file*, multiple *data caches* and a *retire buffer*.

**Frontend and backend.** The frontend is responsible for fetching the flow of instruction bytes to be executed, break it down into operations executable by the backend and issue them

to execution units. The backend, in turn, is responsible for the actual computations made by the processor.

As such, the frontend can be seen as a manager for the backend: the latter actually executes the work, while the former ensures that work is made available to it, orchestrates its execution and scheduling, and ensures each "worker" in the backend is assigned tasks within its skill set.

**Register file.** The register file holds the processor's registers, small amounts of fast memory directly built into the processor's cores, on which computations are made.

**Data caches.** The cache hierarchy (usually L1, L2 and L3) caches data rows from the main memory, whose access latency would slow computation down by several orders of magnitude if it was accessed directly. Usually, the L1 cache resides directly in the computation core, while the L2 and L3 caches are shared between multiple cores.

#### An instruction's walk through the processor

Several CPU cycles may pass from the moment an instruction is first fetched by the processor, until the time this instruction is considered completed and discarded. Let us follow the path of one such instruction through the processor.

The CPU frontend constantly fetches a flow of instruction bytes. This flow must first be broken down into a sequence of instructions. While on some ISAs, each instruction is made of a constant amount of bytes — eg. ARM —, this is not always the case: for instance, x84-64 instructions can be as short as one byte, while the ISA only limits an instruction to 15 bytes [23c]. This task is performed by the *decoder*, which usually outputs a flow of *micro-operations*, or  $\mu$ OPs.

Some microarchitectures rely on complex decoding phases, first splitting instructions into *macro-operations*, to be split again into  $\mu$ OPs further down the line. Part of this decoding may also be cached, *eg.* to optimize loop decoding, where the same sequence of instructions will be decoded many times.

Microarchitectures typically implement more physical registers in their register file than the ISA exposes to the programmer. The CPU takes advantage of those additional registers by including a *renamer* in the frontend, to which the just-decoded operations are fed. The renamer maps the ISA-defined registers used explicitly in instructions to concrete registers in the register file. As long as enough concrete registers are available, this phase eliminates certain categories of data dependencies; this aspect is explored briefly below, and later in chapter 5.

Depending on the microarchitecture, the decoded operations — be they macro- or microoperations at this stage — may undergo several more phases, specific to each processor.

Typically, however,  $\mu$ OPs will eventually be fed into a *Reorder Buffer*, or ROB. Today, most consumer- or server-grade CPUs are *out-of-order*, with effects detailed below; the reorder buffer makes this possible. The  $\mu$ OPs may wait for a few cycles in this reorder buffer, before being pulled by the *issuer*.

Finally, the  $\mu$ OPs are *issued* to the backend towards *execution ports*. Each port usually processes at most one  $\mu$ OP per CPU cycle, and acts as a sort of gateway towards the actual execution units of the processor.

Each execution port may be (and usually is) connected to multiple different execution units: for instance, Intel Skylake's port 6 is responsible for both branch  $\mu$ OPs and integer arithmetics; while ARM's Cortex A72 has a single port for both memory loads and stores.

In most cases, execution units are *fully pipelined*, meaning that while processing a single  $\mu$ OP takes multiple cycles, the unit is able to start processing a new  $\mu$ OP every cycle: multiple  $\mu$ OPs are thus being processed, at different stages, during each cycle, akin to a factory's assembly line.

Finally, when a  $\mu$ OP has been entirely processed and exits its processing unit's pipeline, it is committed to the *retire buffer*, marking the  $\mu$ OP as complete.

#### Dependencies handling

In this flow of  $\mu$ OPs, some are dependent on the result computed by a previous  $\mu$ OP — or, rather more precisely, await the change of state induced by a previous  $\mu$ OP. If, for instance, two successive identical  $\mu$ OPs compute  $\%r10 \leftarrow \%r10 + \%r11$ , the second instance must wait for the completion of the first one, as the value of %r10 after the execution of the latter is not known before its completion.

The  $\mu$ OPs that depend on a previous  $\mu$ OP are not *issued* until the latter is marked as completed by entering the retire buffer<sup>1</sup>.

Since computation units are pipelined, they reach their best efficiency only when  $\mu$ OPs can be fed to them in a constant flow. Yet, as such, a dependency may block the computation entirely until its dependent result is computed, throttling down the CPU's performance.

The renamer helps relieving this dependency pressure when the dependency can be broken by simply renaming one of the registers. We detail this later on chapter 5, but such dependencies may be eg. write-after-read: if  $\r11 \leftarrow \r10$  is followed by  $\r10 \leftarrow \r12$ , then the latter must wait for the former's completion, as it would else overwrite  $\r10$ , which is read by the former. However, the second instruction may be renamed to write to  $\r10_{alt}$  instead — also renaming every subsequent read to the same value —, thus avoiding the dependency.

#### Out-of-order vs. in-order processors

When computation is stalled by a dependency, it may however be possible to issue immediately a  $\mu$ OP which comes later in the instruction stream, but depends only on results already available.

For this reason, many processors are now *out-of-order*, while processors issuing  $\mu$ OPs strictly in their original order are called *in-order*. Out-of-order microarchitectures feature a *reorder buffer*, from which instructions are picked to be issued. The reorder buffer acts as a sliding window of microarchitecturally-fixed size over decoded  $\mu$ OPs, from which the oldest  $\mu$ OP whose dependencies are satisfied will be executed. Thus, out-of-order CPUs are only able to execute operations out of order as long as the  $\mu$ OP to be executed is not too far ahead from the oldest  $\mu$ OP awaiting to be issued — specifically, not more than the size of the reorder buffer ahead.

It is also important to note that out-of-order processors are only out-of-order *from a certain* point on: a substantial part of the processor's frontend is typically still in-order.

#### Hardware counters

Many processors provide hardware counters, to help (low-level) programmers understand how their code is executed. The counters available widely depend on each specific processor. The majority of processors, however, offer counters to determine the number of elapsed cycles between two instructions, as well as the number of retired instructions. Some processors further offer counters for the number of cache misses and hits on the various caches, or even the number of  $\mu$ OPs executed on a specific port.

While access to these counters is vendor-dependent, abstraction layers are available: for instance, the Linux kernel abstracts these counters through the **perf** interface, while **PAPI** further attempts to unify similar counters from different vendors under a common name.

<sup>1.</sup> Some processors, however, introduce "shortcuts" when a  $\mu$ OP can yield a result before its full completion. In such cases, while the  $\mu$ OP depended on is not yet complete and retired, the dependant  $\mu$ OP can still be issued.

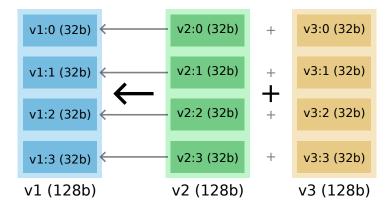

Figure 1.2 – Example of SIMD  $4 \times 32$  bits add instruction on 128 bits

#### SIMD operations

Processors operate at a given *word size*, fixed by the ISA — typically 32 or 64 bits nowadays, even though embedded processors might operate at lower word sizes.

Some instructions, however, operate on chunks of multiple words at once. These instructions are called *vector instructions*, or *SIMD* for Single Instruction, Multiple Data. A SIMD "add" instruction may, for instance, add two chunks of 128 bits, treated each as four integers of 32 bits bundled together, as illustrated in Figure 1.2.

Such instructions present clear efficiency advantages. If the processor is able to handle one such instruction every cycle — even if it is pipelined for multiple cycles —, it multiplies by its number of vector elements the processor's throughput, making it able to process *eg.* four add operations per cycle instead of one, as long as the data is arranged in memory in an appropriate way. Some processors, however, are not able to process the full vector instruction at once, by lack of backend units — it may, for instance, only process two 32-bits adds at once, making the processor able to execute only one such instruction per two cycles. Even in this case, there are clear efficiency benefits: while there is no real gain in the backend, the frontend has only one instruction to decode, rename, etc., greatly alleviating frontend pressure. This is for instance the case of the implementation of the RISC-V [Wat+11] vector extension, supporting up to 256 double-precision floats in a single operation, while the hardware supports far less in one cycle [Man+23; Man23].

## **1.2** Kernel optimization and code analyzers

Optimizing a program, in most contexts, mainly means optimizing it from an algorithmic point of view — using efficient data structures, running some computations in parallel on multiple cores, etc. As pointed out in our introduction, though, optimizations close to the machine's microarchitecture can yield large efficiency benefits, sometimes up to two orders of magnitude [Bon20]. These optimizations, however, are difficult to carry for multiple reasons: they depend on the specific machine on which the code is run; they require deep expert knowledge; they are most often manual, requiring expert time — and thus making them expensive.

Such optimizations are, however, routinely used in some domains. Scientific computation — such as ocean simulation, weather forecast, ... — often rely on the same operations, implemented by low-level libraries optimized in such a way, such as OpenBLAS [Xia; Wan+13] or Intel's MKL [Int03], implementing low-level math operations, such as linear algebra. Machine learning applications, on the other hand, may typically be trained for extensive periods of time, on many cores and accelerators, on a well-defined hardware, with small portions of code being executed many times on different data; as such, they are very well suited for such specific and low-level optimizations.

When optimizing those short fragments of code whose efficiency is critical, or *computation kernels*, insights on what limits the code's performance, or *performance bottlenecks*, are precious to the expert. These insights can be gained by reading the processor's hardware counters, described above in section 1.1.2, typically accurate but of limited versatility. Specialized profilers, such as Intel's VTune [Inta], integrate these counters with profiling to derive further performance metrics at runtime.

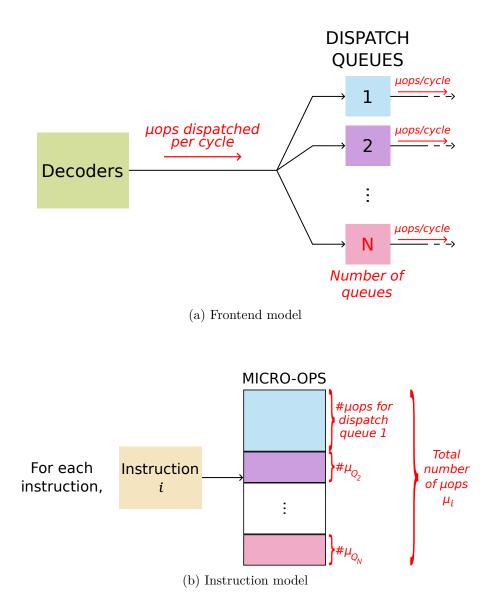

#### 1.2.1 Code analyzers

Another approach is to rely on *code analyzers*, pieces of software that analyze a code fragment — typically at assembly or binary level —, and provide insights on its performance metrics on a given hardware. Code analyzers thus work statically, that is, without executing the code.

**Common hypotheses.** Code analyzers operate under a set of common hypotheses, derived from the typical intended usage.

The kernel analyzed is expected to be the body of a loop, or nest of loops, that should be iterated many times enough to be approximated by an infinite loop. The kernel will further be analyzed under the assumption that it is in *steady-state*, and will thus ignore startup or border effects occurring in extremal cases. As the kernels analyzed are those worth optimizing manually, it is reasonable to assume that they will be executed many times, and focus on their steady-state.

The kernel is further assumed to be L1-resident, that is, to work only on data that resides in the L1 cache. This assumption is reasonable in two ways. First, if data must be fetched from farther caches, or even the main memory, these fetch operations will be multiple orders of magnitude slower than the computation being analyzed, making it useless to optimize this kernel for CPU efficiency — the expert should, in this case, focus instead on data locality, prefetching, etc. Second, code analyzers typically focus only on the CPU itself, and ignore memory effects. This hypothesis formalizes this focus; code analyzers metrics are thus to be regarded assuming the CPU is the bottleneck.

Code analyzers also disregard control flow, and thus assume the code to be *straight-line code*: the kernel analyzed is considered as a sequence of instructions without influence on the control flow, executed in order, and jumping unconditionally back to the first instruction after the last — or, more accurately, the last jump is always assumed taken, and any control flow instruction in the middle is assumed not taken, while their computational cost is accounted for.

Metrics produced. The insights they provide as an output vary with the code analyzer used. All of them are able to predict either the throughput or reciprocal throughput — defined below — of the kernel studied, that is, how many cycles one iteration of the loop takes, in average and in steady-state. Although throughput can already be measured at runtime with hardware counters, a static estimation — if reliable — is already an improvement, as a static analyzer is typically faster than running the actual program under profiling.

Each code analyzer relies on a model, or a collection of models, of the hardware on which it provides analyzes. Depending on what is, or is not modelled by a specific code analyzer, it may further extract any available and relevant metric from its model: whether the frontend is saturated, which computation units from the backend are stressed and by which precise instructions, when the CPU stalls and why, etc. Code analyzers may further point towards the resources that are limiting the kernel's performance, or *bottlenecks*.

**Static vs. dynamic analyzers.** Tools analyzing code, and code analyzers among them, are generally either performing *static* or *dynamic* analyses. Static analyzers work on the program itself, be it source code, assembly or any representation, without running it; while dynamic

analyzers run the analyzed program, keeping it under scrutiny through either instrumentation, monitoring or any relevant technique. Some analyzers mix both strategies to further refine their analyses. As a general rule of thumb, dynamic analyzers are typically more accurate, being able to study the actual execution trace (or traces) of the program, but are significantly slower due to instrumentation's large overhead and focus more on the general, average case than on edge cases.

As most code analyzers are static, this manuscript largely focuses on static analysis. The only dynamic code analyzer we are aware of is **Gus**, described more thoroughly in section 1.3 later, trading heavily run time to gain in accuracy, especially regarding data dependencies that may not be easily obtained otherwise.

**Input formats used.** The analyzers studied in this manuscript all take as input either assembly code, or assembled binaries.

In the case of assembly code, as for instance with llvm-mca, analyzers take either a short assembly snippet, treated as straight-line code and analyzed as such; or longer pieces of assembly, part or parts of which being marked for analysis by surrounding assembly comments.

In the case of assembled binaries, as all analyzers were run on Linux, executables or object files are ELF files. Some analyzers work on sections of the file defined by user-provided offsets in the binary, while others require the presence of *IACA markers* around the code portion or portions to be analyzed. Those markers, introduced by IACA as C-level preprocessor statements, consist in the following x86 assembly snippets:

| 1 mov ebx, | 111        | 1 mov ebx,        | 222        |

|------------|------------|-------------------|------------|

| 2 db 0x64, | 0x67, 0x90 | 2 <b>db</b> 0x64, | 0x67, 0x90 |

|            |            |                   |            |

#### IACA start marker

#### IACA end marker

On UNIX-based operating systems, the standard format for assembled binaries — either object files (..) or executables — is ELF [Com+95]. Such files are organized in sections, the assembled instructions themselves being found in the .text section — the rest holding metadata, program data (strings, icons, ...), debugging information, etc. When an ELF is loaded to memory for execution, each segment may be *mapped* to a portion of the address space. For instance, if the .text section has 1024 bytes, starting at offset 4096 of the ELF file itself, it may be mapped at virtual address 0x454000; as such, the byte that could be read from the program by dereferencing address 0x454010 would be the 16<sup>th</sup> byte from the .text section, that is, the byte at offset 4112 in the ELF file.

Throughout the ELF file, *symbols* are defined as references, or pointers, to specific offsets or chunks in the file. This mechanism is used, among others, to refer to the program's function. For instance, a symbol main may be defined, that would point to the offset of the first byte of the main function, and may also hold its total number of bytes.

Both these mechanisms can be used to identify, without IACA markers or the like, a section of ELF file to be analyzed: an offset and size in the .text section can be provided (which can be found with tools like objdump), or a symbol name can be provided, if an entire function is to be analyzed.

#### 1.2.2 Examples with llvm-mca

We have now covered enough of the theoretical background to introduce code analyzers in a concrete way, through examples of their usage. For this purpose, we use <code>llvm-mca</code>, one of the state-of-the-art code analyzers.

Due to its relative simplicity — at least compared to *eg.* Intel's x86-64 implementations —, we will base the following examples on ARM's Cortex A72, which we introduce in depth later in chapter 3. No specific knowledge of this microarchitecture is required to understand the following examples; for our purposes, if suffices to say that:

- the A72 has a single load port, a single store port and two integer arithmetics ports;

- the xN registers are 64-bits registers;

- the ldr instruction (load register) loads a value from memory into a register;

- the str instruction (store register) stores the value of a register to memory;

- the add instruction adds integer values from its two last operands and stores the result in the first.

Simple example: a single load. We first start by running llvm-mca on a single load operation: ldr x1, [x2].

```

1 $ echo 'ldr x1, [x2]' | llvm-mca --march=aarch64 --mcpu=cortex-a72 -

2 Iterations:

100

3 Instructions:

100

106

4 Total Cycles:

5 Total uOps:

100

7 Dispatch Width:

3

8 uOps Per Cycle:

0.94

9 IPC:

0.94

10 Block RThroughput: 1.0

13 Instruction Info:

14 [1]: #uOps

15 [2]: Latency

16 [3]: RThroughput

[4]: MayLoad

[5]: MayStore

18

19 [6]: HasSideEffects (U)

[2]

[3]

[4]

[5]

[6]

21 [1]

Instructions:

4

1.00

ldr

x1, [x2]

1

*

23

25 Resources:

26 [0]

- A57UnitB

27 [1.0] - A57UnitI

28 [1.1] - A57UnitI

29 [2]

- A57UnitL

30 [3]

- A57UnitM

31 [4]

- A57UnitS

32 [5]

- A57UnitW

[6]

- A57UnitX

33

35

36 Resource pressure per iteration:

[0]

[1.0] [1.1]

[2]

[3]

[4]

[5]

[6]

1.00

_

39

40 Resource pressure by instruction:

[0]

[1.0]

[1.1]

[2]

[3]

[4]

[5]

[6]

41

Instructions:

1.00

42

ldr

x1, [x2]

```

The first rows (2-10) are high-level metrics. 11vm-mca works by simulating the execution of the kernel — here, 100 times, as seen row 2 —. This simple kernel contains only one instruction, which breaks down into a single  $\mu$ OP. Iterating it takes 106 cycles instead of the expected 100 cycles, as this execution is *not* in steady-state, but accounts for the cycles from the decoding of the first instruction to the retirement of the last.

Row 7 indicates that each cycle, the frontend can issue at most 3  $\mu$ OPs. The next two rows are simple ratios. Row 10 is the block's *reverse throughput*, which we will note  $\overline{\mathcal{K}}$  and formalize

later in section 1.2.3, but is roughly defined as the number of cycles a single iteration of the kernel takes.

The next section, *instruction info*, lists data about the instructions present.

Finally, the last section, *resources*, breaks down individual instructions into load incurred on execution ports, first aggregating it by full iteration of the kernel, then instruction by instruction. The maximal load of each port is normalized to 1, which amounts to say that it is expressed in number of cycles required to process the load.

Here, the only pressure is 1 on the port labeled [2], that is, the load port. Thus, the kernel cannot complete in less than a full cycle, as it takes up all load resources available.

The timeline mode. Another useful view that can be displayed by llvm-mca is its timeline mode, enabled by passing an extra --timeline flag. In the previous example, it further outputs:

| 1  | Timeline | view:         |    |     |          |

|----|----------|---------------|----|-----|----------|

| 2  |          | 01234         | 15 |     |          |

| 3  | Index    | 0123456789    |    |     |          |

| 4  |          |               |    |     |          |

| 5  | [0,0]    | DeeeeER .     |    | ldr | x1, [x2] |

| 6  | [1,0]    | D=eeeeER .    |    | ldr | x1, [x2] |

| 7  | [2,0]    | D==eeeeER .   |    | ldr | x1, [x2] |

| 8  | [3,0]    | .D==eeeeER.   |    | ldr | x1, [x2] |

| 9  | [4,0]    | .D===eeeeER   |    | ldr | x1, [x2] |

| 10 | [5,0]    | .D===eeeeER   |    | ldr | x1, [x2] |

| 11 | [6,0]    | . D===eeeeER  |    | ldr | x1, [x2] |

| 12 | [7,0]    | . D====eeeeER |    | ldr | x1, [x2] |

| 13 | [8,0]    | . D====eeeeEH | ٤. | ldr | x1, [x2] |

| 14 | [9,0]    | . D====eeeel  | ER | ldr | x1, [x2] |

which indicates, for each instruction, the timeline of its execution. Here, D stands for decode, e for being executed — in the pipeline —, E for last cycle of its execution — leaving the pipeline —, R for retiring. When an instruction is decoded and waiting to be dispatched to execution, an = is shown.

The identifier at the beginning of each row indicates the kernel iteration number, and the instruction within.

Here, we can better understand the 106 cycles seen earlier: it takes a first cycle to decode the first instruction, the instruction remains in the pipeline for 5 cycles, and must finally be retired. In steady-state, however, the instruction would be already decoded (while a previous instruction was being executed), the retirement would also be taking place while another instruction executes, and the pipeline would be accepting new instructions for four of these five cycles. We can thus avoid using up 6 of those 106 cycles in steady-state, taking us back to the expected 100 cycles.

**Single integer add.** If we substitute this load operation with an integer add operation, we find a reverse throughput halved:

```

1 $ echo 'add x1,x2,x3' | llvm-mca --march=aarch64 --mcpu=cortex-a72 -

2 Iterations:

100

100

3 Instructions:

4 Total Cycles:

53

5 Total uOps:

100

7 Dispatch Width:

3

8 uOps Per Cycle:

1.89

9 IPC:

1.89

10 Block RThroughput: 0.5

12 [...]

13

```

```

14 [1.0] - A57UnitI

15 [1.1] - A57UnitI

16

17 [...]

18

19 Resource pressure by instruction:

[1.0]

[1.1]

[2]

[5]

[6]

Instructions:

20 [O]

[3]

[4]

0.50

0.50

add

21

_

x1, x2, x3

_

_

22

23 Timeline view:

24 Index

01234567

26 [0,0]

DeER . .

add

x1, x2, x3

27 [1,0]

DeER . .

add

x1, x2, x3

28 [2,0]

D=eER. .

add

x1, x2, x3

29 [3,0]

.DeER. .

add

x1, x2, x3

30 [4,0]

.D=eER .

add

x1, x2, x3

x1, x2, x3

31 [5,0]

.D=eER .

add

x1, x2, x3

32 [6,0]

. D=eER.

add

x1, x2, x3

33 [7,0]

. D=eER.

add

. D == e E R

x1, x2, x3

34 [8,0]

add

35 [9,0]

D=eER

x1, x2, x3

add

```

Indeed, as we have two integer arithmetics unit, two adds may be executed in parallel, as can be seen in the timeline view.

Load and two adds. If we combine those two instructions in a kernel with a single load and two adds, we obtain a kernel that still fits in the execution ports in a single cycle. llvm-mca confirms this:

```

1 $ echo -e 'ldr x1,[x2]

2 add x3,x4,x5

3 add x6,x7,x8' | llvm-mca --march=aarch64 --mcpu=cortex-a72 -

100

5 Iterations:

6 Instructions:

300

106

7 Total Cycles:

8 Total uOps:

300

9

10 Dispatch Width:

3

11 uOps Per Cycle:

2.83

12 IPC:

2.83

13 Block RThroughput: 1.0

14

15 [...]

16

17 Resource pressure per iteration:

18 [0]

[1.0]

[1.1]

[2]

[4]

[5]

[6]

[3]

1.00

1.00

1.00

19

20

21 Resource pressure by instruction:

[1.0]

[1.1]

[2]

[3]

[4]

[5]

[6]

Instructions:

22 [O]

1.00

ldr

x1, [x2]

23

_

-

_

-

_

1.00

_

_

_

_

_

add

x3, x4, x5

_

25

-

1.00

_

_

add

x6, x7, x8

```

We can indeed see that an iteration fully utilizes the three ports, but still fits: the kernel still manages to have a reverse throughput of 1.

```

1 $ echo -e 'add x1, x2, x3

2 \text{ add } x4, x5, x6

3 add x7,x8,x9' | llvm-mca --march=aarch64 --mcpu=cortex-a72 --timeline -

5 Iterations:

100

6 Instructions:

300

153

7 Total Cycles:

8 Total uOps:

300

9

10 Dispatch Width:

3

11 uOps Per Cycle:

1.96

12 IPC:

1.96

13 Block RThroughput: 1.5

14

15 [...]

17 Resource pressure per iteration:

[1.1] [2]

[5]

[6]

[4]

18 [0]

[1.0]

[3]

1.50

1.50

19

_

_

_

_

20

21 Resource pressure by instruction:

22 [O]

[1.0]

[1.1]

[2]

[3]

[4]

[5]

[6]

Instructions:

23

0.50

0.50

_

_

add

x1, x2, x3

-

0.50

0.50

_

-

_

_

_

24

add

x4, x5, x6

_

0.50

0.50

25

_

_

_

_

add

x7, x8, x9

26

27

28 Timeline view:

01234567

29

0123456789

30 Index

31

32 [0,0]

DeER .

x1, x2, x3

add

. .

.

33 [0,1]

DeER .

add

x4, x5, x6

.

. .

34 [0,2]

D=eER.

add

x7, x8, x9

.

. .

35 [1,0]

.DeER.

add

x1, x2, x3

. .

.

36 [1,1]

.D=eER

add

x4, x5, x6

. .

.

37 [1,2]

.D=eER

add

x7, x8, x9

. .

.

38 [...]

```

**Three adds.** A kernel of three adds, however, will not be able to run in a single cycle:

The resource pressure by iteration view confirms that we exceed the integer arithmetic capacity of the processor for a single cycle. This is correctly reflected in the timeline view: the instruction [0,2] starts executing only at cycle 3, along with [1,0].

Load, store and two adds. A kernel of one load, two adds and one store should, ports-wise, fit in a single cycle. However, llvm-mca finds for this kernel a reverse throughput of 1.3:

```

1 $ echo -e 'ldr x1,[x2]

2 add x3,x4,x5

3 add x6,x7,x8

4 str x9, [x10] ' | llvm-mca --march=aarch64 --mcpu=cortex-a72 --timeline -

100

6 Iterations:

7 Instructions:

400

8 Total Cycles:

139

9 Total uOps:

400

11 Dispatch Width:

3

12 uOps Per Cycle:

2.88

13 IPC:

2.88

14 Block RThroughput: 1.3

```

```

16 [...]

17

18 Resource pressure per iteration:

[1.0]

[1.1]

[2]

[4]

[5]

[6]

19 [0]

[3]

1.00

1.00

1.00

1.00

_

21

22 Resource pressure by instruction:

[1.1]

[2]

[3]

[5]

[6]

23

[0]

[1.0]

[4]

Instructions:

1.00

ldr

x1, [x2]

_

-

_

-

-

_

_

1.00

_

_

_

_

add

x3, x4, x5

_

_

1.00

_

add

x6, x7, x8

-

26

_

_

_

1.00

str

x9, [x10]

30 Timeline view:

012345678

32 Index

0123456789

x1, [x2]

34 [0,0]

DeeeeER

ldr

DeE---R

x3, x4, x5

35 [0,1]

.

.

.

add

DeE---R

36 [0,2]

x6, x7, x8

.

.

.

add

37 [0,3]

.DeE--R

x9, [x10]

str

.

.

.

38 [1,0]

.DeeeeER

x1, [x2]

ldr

.

.

.

.DeE---R

39 [1,1]

add

x3, x4, x5

.

.

.

40 [1,2]

. DeE--R

x6, x7, x8

add

.

.

41 [1,3]

. DeE--R

x9, [x10]

str

```

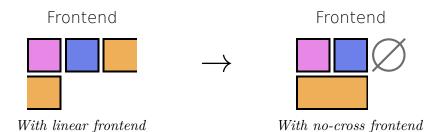

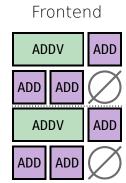

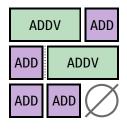

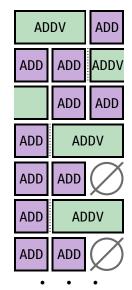

While the resource pressure views confirm that the ports are able to handle this kernel in a single cycle, the timeline shows that it is in fact the frontend that stalls the computation. As only three instructions may be decoded and issued per cycle, the backend is not fed with enough instructions per cycle to reach a reverse throughput of 1.

#### 1.2.3 Definitions

#### Throughput and reciprocal throughput

Given a kernel  $\mathcal{K}$  of straight-line assembly code, we have referred to  $\overline{\mathcal{K}}$  as the *reciprocal* throughput of  $\mathcal{K}$ , that is, how many cycles  $\mathcal{K}$  will require to complete its execution in steady-state. We define this notion here more formally.

Notation  $(\mathcal{K}^n)$

Given a kernel  $\mathcal{K}$  and a positive integer  $n \in \mathbb{N}^*$ , we note  $\mathcal{K}^n$  the kernel  $\mathcal{K}$  repeated n times, that is, the instructions of  $\mathcal{K}$  concatenated n times.

#### **Definition** $(C(\mathcal{K}))$

The number of cycles of a kernel  $\mathcal{K}$  is defined, in steady-state, as the number of elapsed cycles from the moment the first instruction of  $\mathcal{K}$  starts to be decoded to the moment the last instruction of  $\mathcal{K}$  is issued.

We note  $C(\mathcal{K})$  the number of cycles of  $\mathcal{K}$ .

We extend this definition so that  $C(\emptyset) = 0$ ; however, care must be taken that, as we work in steady-state, this  $\emptyset$  must be *in the context of a given kernel* (*ie.* we run  $\mathcal{K}$ until steady-state is reached, then consider how many cycles it takes to execute 0 further instructions). This context is clarified by noting  $C(\mathcal{K}^0)$ . Due to the pipelined nature of execution units, this means that the same instruction of each iteration of  $\mathcal{K}$  will be retired — *ie.* yield its result — every steady-state execution time. For this reason, the execution time is measured until the last instruction is issued, not retired.

**Lemma** (*Periodicity of*  $C(\mathcal{K}^{n+1}) - C(\mathcal{K}^n)$ )

Given a kernel  $\mathcal{K}$ , the sequence  $(C(\mathcal{K}^{n+1}) - C(\mathcal{K}^n))_{n \in \mathbb{N}}$  is periodic, that is, there exists  $p \in \mathbb{N}^*$  such that

$$\forall n \in \mathbb{N}, C\left(\mathcal{K}^{n+1}\right) - C\left(\mathcal{K}^n\right) = C\left(\mathcal{K}^{n+p+1}\right) - C\left(\mathcal{K}^{n+p}\right)$$

We note this period  $\mathcal{P}(\mathcal{K})$ .

*Proof.* The number of CPU resources that can be shared between instructions in a processor is finite (and relatively small, usually on the order of magnitude of 10). These resources are typically the number of  $\mu$ OPs issued for each port in the current cycle, the number of decoded instructions, total number of issued  $\mu$ OPs this cycle and such.

For each of these resources, their number of possible states is also finite (and also small). Thus, the total number of possible states of a processor at the end of a kernel iteration cannot be higher than the combination of those states.

For a given kernel  $\mathcal{K}$ , We note  $\sigma(\mathcal{K})$  the CPU state reached after executing  $\mathcal{K}$ , in steady-state.

Given a kernel  $\mathcal{K}$ , the set  $\{\sigma(\mathcal{K}^n), n \in \mathbb{N}\}$  is a subset of the total set of possible states of the processor, and is thus finite — and, in all realistic cases, is usually way smaller than the full set, given that only a portion of those resources are used by a kernel.

We further note that, for all  $n \in \mathbb{N}$ ,  $\sigma(\mathcal{K}^{n+1})$  is function of only the processor considered,  $\mathcal{K}$  and  $\sigma(\mathcal{K}^n)$ : indeed, a steady-state for  $\mathcal{K}^n$  is also a steady-state for  $\mathcal{K}^{n+1}$  and, knowing  $\sigma(\mathcal{K}^n)$ , the execution can be continued for the following  $\mathcal{K}$ , reaching  $\sigma(\mathcal{K}^{n+1})$ .

Thus, by the pigeon-hole principle, there exists  $p \in \mathbb{N}$  such that  $\sigma(\mathcal{K}) = \sigma(\mathcal{K}^{p+1})$ . By induction, as each state depends only on the previous one, we thus obtain that  $(\sigma(\mathcal{K}^n))_n$  is periodic of period p. As we consider only the execution's steady state, the sequence is periodic from rank 0.

As the number of cycles needed to execute  $\mathcal{K}$  only depend on the initial state of the processor, we thus have

$$\forall n \in \mathbb{N}, C\left(\mathcal{K}^{n+1}\right) - C\left(\mathcal{K}^n\right) = C\left(\mathcal{K}^{n+p+1}\right) - C\left(\mathcal{K}^{n+p}\right)$$

#### **Definition** (*Reciprocal throughput of a kernel*)

The reciprocal throughput of a kernel  $\mathcal{K}$ , noted  $\overline{\mathcal{K}}$  and measured in cycles per iteration, is also called the steady-state execution time of a kernel.

We note  $p = \mathcal{P}(\mathcal{K}) \in \mathbb{N}^*$  the period of  $C(\mathcal{K}^{n+1}) - C(\mathcal{K}^n)$  (by the above lemma), and define

$$\overline{\mathcal{K}} = \frac{C\left(\mathcal{K}^p\right)}{p}$$

We define this as the average on a whole period because subsequent kernel iterations may "share" a cycle.

#### Example

Let  $\mathcal{K}$  be a kernel of three instructions, and assume that a given processor can only issue two instructions per cycle, but has no other bottleneck for  $\mathcal{K}$ . Then,  $C(\mathcal{K}) = 2$ , as three instructions cannot be issued in a single cycle; yet  $C(\mathcal{K}^2) = 3$ , as six instructions can be issued in only three cycles. In this case, the period p is clearly 2. Thus, in this case,  $\overline{\mathcal{K}} = 1.5$ .

#### Remark

As  $C(\mathcal{K})$  depends on the microarchitecture of the processor considered, the throughput  $\overline{\mathcal{K}}$  of a kernel  $\mathcal{K}$  implicitly depends on the processor considered.

#### Lemma

Let  $\mathcal{K}$  be a kernel and  $p = \mathcal{P}(\mathcal{K})$ . For all  $n \in \mathbb{N}$  such that n = kp + r, with  $k, r \in \mathbb{N}$ ,  $1 \le r \le p$ ,

$$C\left(\mathcal{K}^{n}\right) = kC\left(\mathcal{K}^{p}\right) + C\left(\mathcal{K}^{r}\right)$$

*Proof.* From the previous lemma instantiated with n = 0, we have

$$C\left(\mathcal{K}^{1}\right) - C\left(\mathcal{K}^{0}\right) = C\left(\mathcal{K}^{p+1}\right) - C\left(\mathcal{K}^{p}\right)$$

$$\iff C\left(\mathcal{K}^{p}\right) = C\left(\mathcal{K}^{p+1}\right) - C\left(\mathcal{K}^{1}\right)$$

and thus by induction,  $\forall m \in \mathbb{N}, C(\mathcal{K}^{m+p}) - C(\mathcal{K}^m) = C(\mathcal{K}^p).$

Thus, if k = 0, the property is trivial. If k = 1, it is a direct application of the above:

$$C\left(\mathcal{K}^{p+r}\right) = C\left(\mathcal{K}^{p}\right) + C\left(\mathcal{K}^{r}\right)$$

We prove by induction the cases for k > 1.

#### Lemma

Given a kernel  $\mathcal{K}$ ,

$$\frac{C(\mathcal{K}^n)}{n} \xrightarrow[n \to \infty]{} \overline{\mathcal{K}}$$

Furthermore, this convergence is linear:

$$\left|\frac{C\left(\mathcal{K}^{n}\right)}{n} - \overline{\mathcal{K}}\right| = \mathcal{O}\left(\frac{1}{n}\right)$$

*Proof.* Let  $n \in \mathbb{N}^*$  and  $p = \mathcal{P}(\mathcal{K}) \in \mathbb{N}^*$  the periodicity by the above lemma. Let  $k, r \in \mathbb{N}^*$  such that  $n = kp + r, 1 \leq r \leq p$ .

$$C(\mathcal{K}^{n}) = k \cdot C(\mathcal{K}^{p}) + C(\mathcal{K}^{r}) \qquad (by \ lemma)$$

$$= kp \frac{C(\mathcal{K}^{p})}{p} + C(\mathcal{K}^{r})$$

$$= kp \overline{\mathcal{K}} + C(\mathcal{K}^{r})$$

$$\implies \left| C(\mathcal{K}^{n}) - n\overline{\mathcal{K}} \right| = \left| kp \overline{\mathcal{K}} + C(\mathcal{K}^{r}) - (kp + r)\overline{\mathcal{K}} \right|$$

$$= \left| C(\mathcal{K}^{r}) - r\overline{\mathcal{K}} \right|$$

$$\leq C(\mathcal{K}^{r}) + r\overline{\mathcal{K}} \qquad (all \ is \ positive)$$

$$\leq \left( \max_{m \leq p} C(\mathcal{K}^{m}) \right) + p\overline{\mathcal{K}}$$

This last right-hand expression is independent of n, which we note M. Dividing by n, we obtain

$$\left|\frac{C\left(\mathcal{K}^{n}\right)}{n} - \overline{\mathcal{K}}\right| \le \frac{M}{n}$$

from which both results follow.

Throughout this manuscript, we mostly use reciprocal throughput as a metric, as we find it more relevant from an optimisation point of view — an opinion we detail in chapter 4. However, the *throughput* of a kernel is most widely used in the literature in its stead.

#### **Definition** (*Throughput of a kernel*)

The throughput of a kernel  $\mathcal{K}$ , measured in instructions per cycle, or IPC, is defined as the number of instructions in  $\mathcal{K}$ , divided by the steady-state execution time of  $\mathcal{K}$ :

$$\mathrm{IPC}(\mathcal{K}) = \frac{|\mathcal{K}|}{\overline{\mathcal{K}}}$$

In the literature or in analyzers' reports, the throughput of a kernel is often referred to as its IPC (its unit).

Notation (Experimental measure of  $\overline{\mathcal{K}}$ )

We note  $\overline{\mathcal{K}}^{M(n)}$  the experimental measure of  $\mathcal{K}$ , realized by:

- sampling the hardware counter of total number of instructions retired and the counter of total number of cycles elapsed,

- executing  $\mathcal{K}^n$ ,

- sampling again the same counters, and noting respectively  $\Delta_n$  ret and  $\Delta_n C$  their differences,

- noting  $\overline{\mathcal{K}}^{M(n)} = \frac{\Delta_n C \cdot |\mathcal{K}|}{\Delta_n \text{ret}}$ , where  $|\mathcal{K}|$  is the number of instructions in  $\mathcal{K}$ .

#### Lemma

For any kernel  $\mathcal{K}, \overline{\mathcal{K}}^{M(n)} \xrightarrow[n \to \infty]{} \overline{\mathcal{K}}.$

*Proof.* For an integer number of kernel iterations n,  $\Delta_n^{\text{ret}}/|\mathcal{K}| = n$ . While measurement errors may make  $\Delta_n$  ret fluctuate slightly, this fluctuation will be below a constant threshold.

$$\left|\frac{\Delta_n \mathrm{ret}}{|\mathcal{K}|} - n\right| \le E_{\mathrm{ret}}$$

The same way, and due to the pipelining effects we noted below the definition of  $\overline{\mathcal{K}}$ ,

$$|\Delta_n C - C(\mathcal{K}^n)| \le E_C$$

with  $E_C$  a constant.

As those errors are constant, while other quantities are linear, we thus have

$$\overline{\mathcal{K}}^{M(n)} = \frac{\Delta_n C}{\Delta_n ret/|\mathcal{K}|} \xrightarrow[n \to \infty]{} \frac{C(\mathcal{K}^n)}{n}$$

and, composing limits with the previous lemma, we thus obtain

$$\overline{\mathcal{K}}^{M(n)} \xrightarrow[n \to \infty]{} \overline{\mathcal{K}}$$

Given this property, we will use  $\overline{\mathcal{K}}$  to refer to  $\overline{\mathcal{K}}^{M(n)}$  for large values of n in this manuscript whenever it is clear that this value is a measure.

#### Basic block of an assembly-level program

Code analyzers are meant to analyze sections of straight-line code, that is, portions of code which do not contain control flow. As such, it is convenient to split the program into *basic blocks*, that is, portions of straight-line code linked to other basic blocks to reflect control flow. We define this notion here formally, to use it soundly in the following chapters of this manuscript.

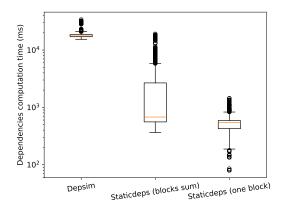

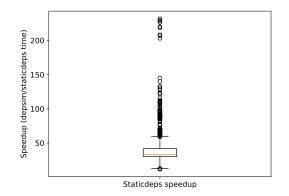

#### Notation